فلیپ فلاپ Master-Slave JK:

فلیپ فلاپ Master-Slave JK با استفاده از دو فلیپ فلاپ SR که به صورت پشت سر هم (سری) متصل شده است، مشکل زمان بندی فلیپ فلاپ های JK معمولی را برطرف می کند.

فلیپ فلاپ اول به عنوان Master یا فرمانده عمل می کند و حساس به لبه های بالارونده سیگنال ساعت است.

اما فلیپ فلاپ دوم به عنوان Slave یا فرمان بر عمل کرده و حساس به لبه های پایین رونده سیگنال ساعت است.

این امر باعث می شود فلیپ فلاپ Master-Slave JK در دو مرحله تغییر وضعیت پیدا کند که هر مرحله آن وابسته به نیم سیکل های متفاوت سیگنال ساعت هستند.

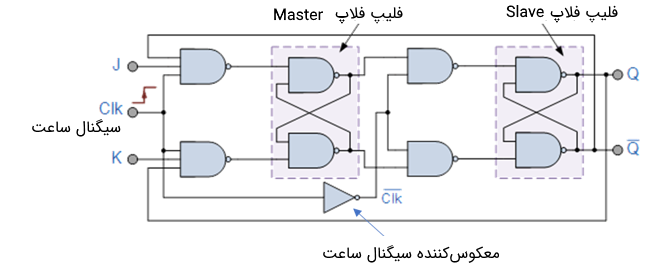

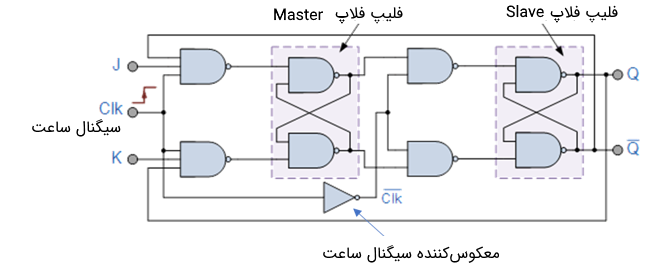

شکل زیر بلوک دیاگرام فلیپ فلاپ Master-Slave JK را نشان می دهد.

مطابق شکل بالا خروجی های فلیپ فلاپ Master به عنوان ورودی های فلیپ فلاپ Slave استفاده می شوند. همچنین خروجی های فلیپ فلاپ Slave نیز به ورودی فلیپ فلاپ Master فیدبک شده است.

برای اینکه دو فلیپ فلاپ در دو لبه مختلف سیگنال ساعت عمل کنند، از یک گیت NOT به عنوان معکوس کننده سیگنال ساعت استفاده می شود.

این بلوک باعث می شود که فلیپ فلاپ Slave وابسته به لبه پایین رونده سیگنال ساعت شود در حالی که فلیپ فلاپ Master وابسته به لبه بالارونده آن است.

در ادامه به این مطلب می پردازیم که این مدار چگونه می تواند مشکل Race در فلیپ فلاپ های JK معمولی را رفع کند.

اصول کاری فلیپ فلاپ Master-Slave JK:

به منظور درک بهتر، دقت کنید که بلوک آشکارساز پالس در مدار وجود ندارد و در واقع مدار حساس به سطح است.

پس فلیپ فلاپ Mater حساس به سطح یک منطقی و فلیپ فلاپ Salve حساس به سطح صفر منطقی است.

پس تغییر وضعیت فلیپ فلاپ Maser بر اساس ورودی JK زمانی اتفاق می افتد که سیگنال ساعت در سطح یک منطقی باشد و همچنین تغییر وضعیت فلیپ فلاپ Slave بر اساس ورودی JK زمانی اتفاق می افتد که سیگنال ساعت در سطح صفر منطقی باشد.

مشکل Race زمانی رخ می داد که هر سه ورودی J، K و سیگنال ساعت یک منطقی باشند.

اگر این اتفاق بیفتد، خروجی فلیپ فلاپ Maser تغییر وضعیت پیدا می کند اما به دلیل اینکه خروجی گیت معکوس کننده صفر منطقی می شود، گیت های فلیپ فلاپ Slave فعال نمی شوند و در نتیجه خروجی فلیپ فلاپ Master-Slave JK بدون تغییر باقی می ماند.

برای اینکه تغییر حالت در وضعیت خروجی فلیپ فلاپ Master-Slave JK پیش بیاید، باید خروجی گیت معکوس کننده یک منطقی شود و این امر زمانی اتفاق می افتد که سیگنال ساعت از سطح یک منطقی به سطح صفر منطقی برود.

بنابراین می توان نتیجه گرفت که تغییر وضعیت خروجی فلیپ فلاپ Master-Slave JK تنها زمانی ایجاد می شود که لبه پایین رونده در سیگنال ساعت ایجاد شود و زمانی که سیگنال ساعت ثابت و در وضعیت یک منطقی است، هیچ تغییری در خروجی آن ایجاد نمی شود.

آی سی TTL 74LS73 حاوی دو فلیپ فلاپ JK معمولی است که به دو صورت می توان از آن استفاده کرد.

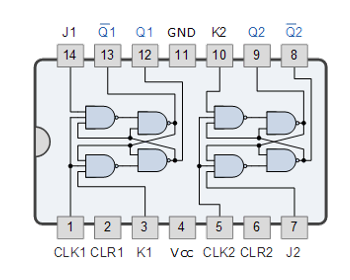

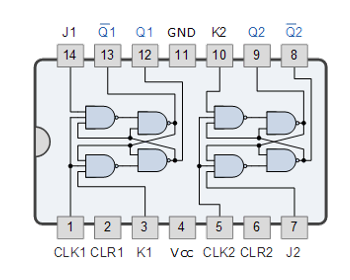

در حالت اول، این آی سی به عنوان دو فلیپ فلاپ JK معمولی استفاده می شود و در حالت دوم با اتصال سری آن ها به عنوان فلیپ فلاپ Master-Slave JK به کار می رود. بلوک دیاگرام این آی سی در شکل زیر نشان داده شده است.

مطابق این شکل پایه های 3، 14، 1 و 12 به ترتیب ورودی های K، J، سیگنال ساعت و خروجی Q فلیپ فلاپ اول هستند.

به همین ترتیب پایه های 7، 10، 5 و 9 به ترتیب ورودی های K، J، سیگنال ساعت و خروجی Q فلیپ فلاپ دوم هستند.

همچنین پایه های 4 و 11 تغذیه و زمین آی سی هستند و پایه های 2 و 6 نیز به منظور Reset کردن فلیپ فلاپ ها بدون توجه به وضعیت منطقی سیگنال های منطقی در ورودی های آن ها به کار می روند.

مشخصات برخی از آی سی های فلیپ فلاپ JK در جدول زیر نشان داده شده است.