شیفت رجیستر 4 بیتی ورودی سریال-خروجی موازی:

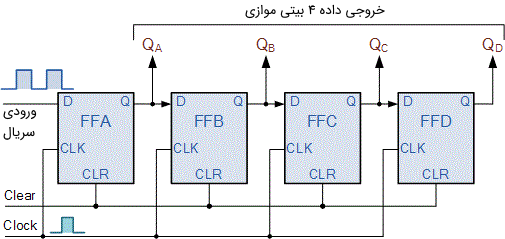

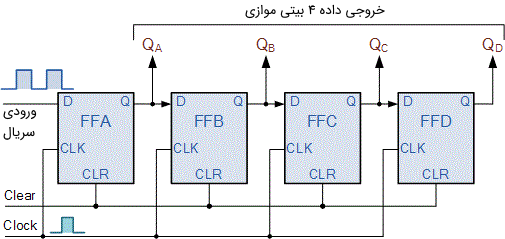

در این قسمت به توضیح نحوه عملکرد این نوع شیفت رجیستر می پردازیم. شکل زیر نمایی از یک شیفت رجیستر 4 بیتی ورودی سریال-خروجی موازی را نشان می دهد.

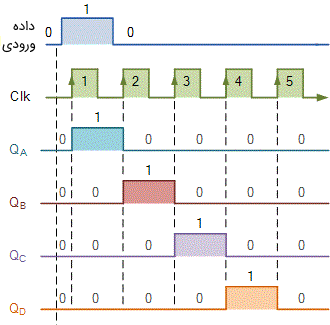

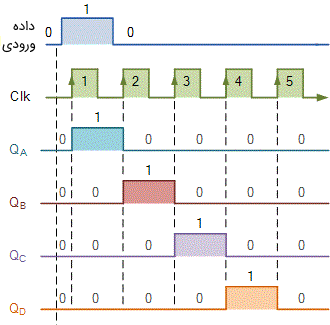

فرض می کنیم که تمام فلیپ فلاپ های FFA تا FFD ریست شده اند و تمام خروجی های QA تا QD در سطح منطقی صفر هستند.

به عبارت دیگر هیچ داده موازی خارج نمی شود. حال اگر یک داده 1 منطقی به پین ورودی فلیپ فلاپ FFA متصل شود، در نتیجهQA متناظر به سطح HIGH یا یک منطقی می رود، در حالی که تمام خروجی های دیگر هنوز در سطح صفر منطقی باقی مانده اند.

حال فرض کنید که پین ورودی داده فلیپ فلاپ FFA دوباره به سطح صفر منطقی بازگشته است (یک پالس ورودی 0-1-0 وارد شده است).

پالس ساعت دوم، سطح خروجی فلیپ فلاپ FFA را به صفر و خروجی فلیپ فلاپ FFB، یعنیQB را به یک منطقی تغییر می دهد، زیرا ورودی این فلیپ فلاپ (یعنی D)، سطح یک منطقی را از خروجی فلیپ فلاپ FFA دریافت کرده است.

بنابراین منطق یک در طول رجیستر یک بار به سمت راست منتقل شده است و در حال حاضر درQA قرار دارد.

زمانی که پالس ساعت سوم به مدار وارد شود، مقدار یک منطقی به خروجی فلیپ فلاپ FFC، یعنیQC

منتقل می شود و این روند تا زمان رسیدن پنجمین پالس ساعت ادامه می یابد. با رسیدن پالس ساعت پنجم، تمام خروجی هایQAتاQD دوباره به سطح منطقی صفر باز می گردند.

تأثیر هر پالس ساعت، انتقال داده مربوط به هر مرحله به اندازه یک واحد به سمت راست است، تا جایی که داده 0001 به صورت کامل در رجیستر ذخیره شود. این مراحل در جدول زیر نشان داده شده است. مقدار این داده اکنون از طریق خروجی هایQAتاQD قابل خوانده شدن است.

بنابراین داده از فرم سریال در ورودی به فرم خروجی موازی تبدیل شده است. جدول درستی و شکل زیر نشان دهنده انتقال عدد یک در طول شیفت رجیستر از چپ به راست است.

توجه کنید بعد از این که پالس ساعت چهارم پایان یافت، چهار بیت داده (0001) در شیفت رجیستر ذخیره می شوند و مشروط بر این که پالس ساعت رجیستر متوقف شده باشد، در آن باقی خواهد ماند.

در عمل، داده ورودی به رجیستر ممکن است از ترکیبات متنوعی از اعداد یک و صفر تشکیل شده باشد. متداول ترین آی سی های SIPO، آی سی های استاندارد هشت بیتی 74LS164 و 74LS594 هستند.