خانه

اپلیکیشن زینگ

آشنایی و همکاری

سامانه صادرات و واردات

فروشگاه

خدمات اطلاعاتی

اخبار و مقالات

تماس با ما

تعریف دیاگرام زمان بندی در مدار:

جدول درستی گاهی اوقات راه درستی برای توصیف رفتار یک مدار ترتیبی مانند فلیپ فلاپ SR نیست.

در این مواقع استفاده از دیاگرام زمان بندی ایده بهتری است:

زیرا نشان می دهد حالت های منطقی در نقاط مختلف در یک مدار در زمان های مختلف چگونه تغیر می کنند.

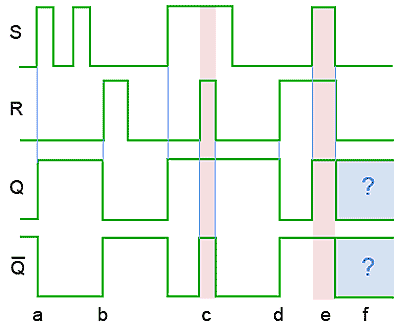

تصویر زیر دیاگرام زمان بندی یک لچ SR را نشان می دهد که نحوه عملکرد این لچ و نیز تغییرات منطقی ورودی های R و S را نشان می دهد.

در زمان a، ورودی S به سطح یک منطقی می رود و خروجی Q را ست می کنند، در نتیجه تا زمان b در سطح یک منطقی باقی می ماند.

در این لحظه ورودی S به سطح LOW تغییر می یابد و ورودی R به سطح یک منطقی برده می شود، در نتیجه خروجی Q ریست می شود.

در طول بازه c، هر دو ورودی R و S در سطح یک منطقی هستند و منجر به ایجاد حالت غیر مجازی می شوند که طی آن خروجی ها هر دو در حالت HIGH قرار می گیرند.

بعد از بازه c، خروجی Q تا زمان d در سطح یک باقی می ماند، که در آن ورودی R به سطح یک منطقی برده می شود و خروجی Q را ریست می کند.

بازه e هم مجددا جزو بازه های غیر مجاز است و در انتها، هر دو ورودی به سطح صفر منطقی می روند و منجر به ایجاد شرایط خروجی تعریف نشده در بازه f می شوند.