خانه

اپلیکیشن زینگ

آشنایی و همکاری

سامانه صادرات و واردات

فروشگاه

خدمات اطلاعاتی

اخبار و مقالات

تماس با ما

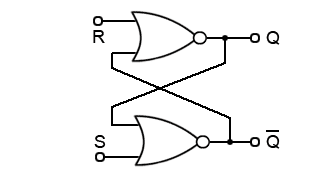

تعریف لچ RS در مدار:

فلیپ فلاپ همچنین می تواند به عنوان مدار لچ (Latch) نیز در نظر گرفته شود؛ زیرا این ادوات می توانند یک تغییر در ورودی خود را به خاطر بسپارند و یا اصطلاحا آن حالت را لچ کنند.

در شکل زیر یک مدار لچ متداول نشان داده شده است. در این مدار ورودی های¯¯¯¯R و ¯¯¯¯S به ورودی های R و S تغییر پیدا کرده اند، به این معنی که این ورودی ها در مدار لچ به صورت Active High هستند.

همچنین محل این ورودی ها نیز تغییر کرده است و ورودی R اکنون به گیتی وارد می شود که خروجی Q دارد و ورودی S متعلق به گیتی است که خروجی آن¯¯¯¯Q است.

دلیل این تغییرات این است که در این مدار به جای گیت NAND از گیت NOR استفاده شده است.

جدول درستی این مدار به صورت زیر است.

ابتدا زمانی که ورودی S به سطح یک منطقی می رود، خروجی Q به مقدار یک ست می شود. این حالت حتی بعد از این که ورودی به حالت صفر منطقی بازگردد نیز در خروجی به خاطر سپرده می شود.

سپس زمانی که ورودی R به یک منطقی ریست شود، خروجی Q نیز به سطح صفر منطقی ریست می شود.

در سطر چهارم، بعد از این که ورودی R دوباره به حالت صفر منطقی بازگردد، حالت قبلی باز هم در خروجی Q به یاد سپرده می شود.

اگر هر دو ورودی در حالت یک منطقی باشند، خروجی Q و¯¯¯¯Q مشابه با یکدیگر خواهند بود. این حالت در واقع غیر مجاز است. زمانی که ورودی ها از حالت 1 و 1 به حالت 0 و 0 تغییر پیدا کنند، حالت خروجی قابل تضمین نخواهد بود.