خانه

اپلیکیشن زینگ

آشنایی و همکاری

سامانه صادرات و واردات

فروشگاه

خدمات اطلاعاتی

اخبار و مقالات

تماس با ما

تعریف مدار صاف کننده ولتاژ کلیدزنی:

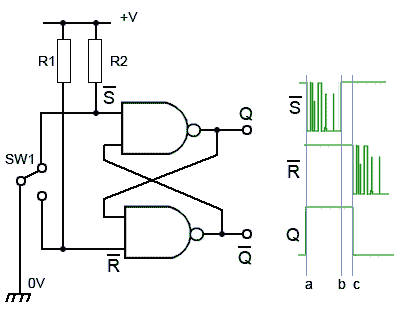

استفاده از فلیپ فلاپ های SR در حذف نوسانات ولتاژ ناشی از کلیدزنی بسیار موثر است. شکل زیر مدار مربوط به استفاده از فلیپ فلاپ SR برای تولید پالس های صاف و تمیز را نشان می دهد.

زمانی که کلید |SW1 مسیر بالایی را به ولتاژ صفر ولت متصل می کند، ورودی¯¯¯¯Sاز منطق یک به منطق صفر تغییر می کند و ورودی¯¯¯¯R از طریق مقاومت پول آپ (Pulled Up) به منبع تغذیه یا منطق یک متصل می شود.

تا زمانی که¯¯¯¯S در منطق صفر باشد (در تصویر با نقطه a نشان داده شده است.)، خروجی Q نیز در منطق یک خواهد بود و از هر پالس اضافی که به دلیل کلیدزنی به وجود آید، صرف نظر می شود.

اما قبل از این که کلید کاملا به اتصال پایینی متصل شود، زمان بسیار کوتاهی (بین لحظات b تا c) هیچکدام از ورودی های ¯¯¯¯S و ¯¯¯¯R به ولتاژ صفر ولت متصل نیستند.

در طول این زمان، ورودی¯¯¯¯S به سطح یک منطقی باز می گردد، بنابراین تا زمان c هر دو ورودی در سطح یک منطقی هستند.

در زمان c، ورودی R توسط کلید به ولتاژ صفر ولت متصل می شود و خروجی Q به مقدار صفر منطقی ریست می شود، در نتیجه پالس خروجی قرینه می شود.

به این روش کلیدزنی Break Before Make می گویند و اهمیت آن نسبت به روش Make Before Break در این است که در روش اول ابتدا اطمینان حاصل می شود که در بازه b تا c که بازه تغییرات است، هر دو ورودی در حالت یک منطقی قرار دارند.

به این صورت از حالت غیرمجاز که در آن هر دو ورودی در حالت صفر قرار دارند، جلوگیری می شود.

با استفاده از این روش می توان اطمینان حاصل کرد که خروجی هایQو¯¯¯¯Q هیچ گاه با هم در یک حالت منطقی قرار نمی گیرند.

همچنین در طول حالت گذار کلید SW1 هر دو ورودی در سطح یک منطقی قرار دارند و به همین دلیل حالت تعریف نشده در جدول درستی بالا ایجاد نمی شود؛ زیرا یکی از ورودی ها همیشه در حالت منطقی صفر قرار دارد، قبل از این که هر دو ورودی به سطح یک بروند.