تعریف فلیپ فلاپ SR در مدار:

فلیپ فلاپ SR یا مدار بای استابل، یکی از اساسی ترین قطعاتی است که ساخت حافظه های کامپیوتری را ممکن ساخت.

فلیپ فلاپ ها همچنین در ساخت بسیاری از مدارات منطقی ترتیبی کاربرد دارند. دو گیت منطقی که به صورت داخلی به یکدیگر متصل شده اند، فرم ساده مدارات فلیپ فلاپی را تشکیل می دهند که خروجی آن ها دارای دو حالت پایدار است.

زمانی که مدار توسط یک پالس ورودی مناسب به یکی از این حالت ها تغییر وضعیت می یابد، تا هنگامی که یک پالس ورودی دیگر به آن وارد نشود و یا منبع تغذیه از مدار قطع نشود، آن وضعیت را حفظ می کند.

به همین دلیل، مدار به عنوان یک لچ بای استابل (Bi-stable Latch) نیز شناخته می شود.

فلیپ فلاپ SR می تواند به عنوان یک حافظه یک بیتی در نظر گرفته شود؛ زیرا پالس ورودی را حتی بعد از عبور آن، نگه می دارد.

انواع مختلف از فلیپ فلاپ ها را می توان با استفاده از گیت های منطقی ساخت. در بین گیت های منطقی مختلف، گیت های NAND و گیت های NOR تطبیق پذیر تر هستند و در بین این دو نیز استفاده از گیت های NAND بسیار رایج تر است.

زیرا علاوه بر این که یک گیت عمومی (Universa) است و اکثر توابع منطقی استاندارد را توسط آن می توان ایجاد کرد، قیمت بسیار پایینی هم دارد. سایر انواع فلیپ فلاپ ها که بسیار پر کاربرد هستند، فلیپ فلاپ های JK و فلیپ فلاپ های D و نیز فلیپ فلاپ نوع T هستند.

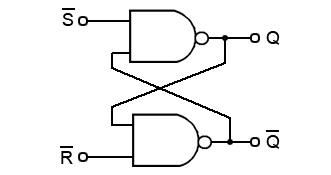

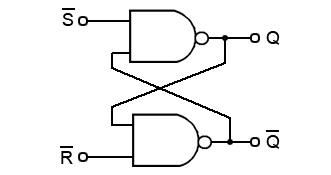

فلیپ فلاپ SR یا فلیپ فلاپ Set-Reset، یکی از ساده ترین مدارات منطقی ترتیبی است و از دو گیت منطقی NAND تشکیل شده است که مطابق شکل زیر به یکدیگر متصل شده اند.

توجه کنید که خروجی هر گیت، به فرم فیدبک مثبت (Positive Feedback) و یا کوپل متقاطع (Cross-Coupling) به یکی از ورودی های گیت دیگر متصل شده است.

مدار دارای دو ورودی Active Low است که توسط نمادهای¯¯¯¯Sو¯¯¯¯Rنشان داده می شوند و نماد خط روی حروف R و S نشان دهنده عملگر NOT منطقی است.

Qو¯¯¯¯Qنیز دو خروجی این مدار هستند. جدول درستی این مدار در زیر آورده شده است و نشان می دهد که با اعمال پالس صفر و یک به ورودی های آن، وضعیت خروجی ها به چه صورت خواهند بود.

در ابتدا با اعمال پالس صفر به ورودی¯¯¯¯S، خروجیQدر یک منطقی تنظیم می شود.

حال با بازگرداندن حالت ورودی¯¯¯¯Sبه یک منطقی، وضعیت خروجی تغییری نخواهد کرد و در واقع پالس صفر توسط مدار به خاطر سپرده می شود.

حال مدار را با اعمال پالس صفر به ورودی¯¯¯¯Rریست می کنیم. با بازگرداندن مقدار¯¯¯¯Rبه یک منطقی، حالت صفر در ورودیQبه خاطر سپرده می شود.