خانه

اپلیکیشن زینگ

آشنایی و همکاری

سامانه صادرات و واردات

فروشگاه

خدمات اطلاعاتی

اخبار و مقالات

تماس با ما

تعریف مسیرداده پردازنده در مدار منطقی:

مسیرداده پردازنده از نظر مفهومی به دو قسمت سازماندهی شده است:

مدارهای ترکیبی:

خروجی مدارهای ترکیبی فقط به مقادیر فعلی ورودی آن ها بستگی دارد. مدارهای ترکیبی به طور مفهومی از گیت های منطقی اساسی ساخته شده اند: گیت AND، گیت OR، گیت NOT و…. خروجی گیت ها در مدارهای ترکیبی هرگز مستقیماً به ورودی های قبلی بازگردانده نمی شود.

گیت های منطقی اساسی را می توان با هم ترکیب کرد و انواع واحدهای سطوح بالاتر را تشکیل داد:

مسیریابی:

مالتی پلکسرها:

دارای چندین سیگنال ورودی داده و یک ورودی کنترل هستند. خروجی با یکی از ورودی ها یکسان است. مقدار سیگنال کنترل تعیین می کند که کدام یک باشد.

دی مالتی پلکسرها:

یک سیگنال ورودی داده، یک ورودی کنترل و چندین سیگنال خروجی دارند. همه سیگنال های خروجی 0 هستند (نادرست) به جز سیگنالی که توسط ورودی کنترل انتخاب شده است. خروجی انتخاب شده مشابه ورودی داده است.

محاسباتی:

جمع کننده های کامل:

یک جمع ستونی باینری را انجام می دهند. این ها بلوک های اصلی اولیه برای جمع و تفریق چندبیتی هستند.

جمع کننده ها و تفریق کننده ها:

دو عدد باینری را جمع یا تفریق می کنند. یک تفریق کننده همان یک جمع کننده با مدارهای اضافی است که عمل مکمل را در یکی از ورودی ها انجام دهد. این مدارها معمولاً طوری طراحی شده اند که علاوه بر جمع یا تفریق مطابق سیگنال کنترلی عمل کنند.

مدار حالت:

در ادامه مدارهای حالت فیلپ فلاپ و رجیستر را معرفی می کنیم.

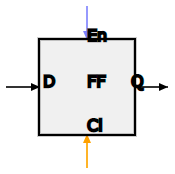

فیلپ فلاپ:

فلیپ فلاپ عنصر اساسی مدار حالت و دارای سه ورودی است:

یک فلیپ فلاپ دارای یک خروجی است:

Q - جدیدترین مقدار داده که در فلیپ فلاپ نوشته شده است.

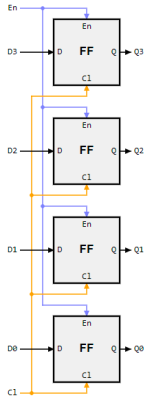

رجیستر:

رجیستر یا ثبات نسخه آنالوگ چندبیتی فلیپ فلاپ است که دارای سه ورودی است:

یک رجیستر دارای یک خروجی است:

این ها همان ورودی ها و خروجی هایی هستند که یک فلیپ فلاپ دارد. تنها تفاوت این است که ورودی D و خروجی Q سیگنال های چندبیتی هستند.

همان طور که در شکل بالا نشان داده شده است، یک رجیستر به عنوان گروهی از فلیپ فلاپ ها اجرا می شود که ساعت خود را به اشتراک می گذارند و سیگنال ها را فعال می کنند.